#### **Science Discovery**

2020; 8(3): 46-51

http://www.sciencepublishinggroup.com/j/sd

doi: 10.11648/j.sd.20200803.11

ISSN: 2331-0642 (Print); ISSN: 2331-0650 (Online)

# Design of a Low Temperature Drift Bandgap Reference Circuit with Second-order Curvature Compensation

Can Guo\*, Rui Xu, Jun Pan

Sichuan Institute of Solid-State Circuits, China Electronics Technology Group Corp., Chongqing, P. R. China

#### Email address:

guoc@mixic.com.cn (Can Guo), xur@mixic.com.cn (Rui Xu), panj@mixic.com.cn (Jun Pan) \*Corresponding author

#### To cite this article:

Can Guo, Rui Xu, Jun Pan. Design of a Low Temperature Drift Bandgap Reference Circuit with Second-order Curvature Compensation. *Science Discovery.* Vol. 8, No. 3, 2020, pp. 46-51. doi: 10.11648/j.sd.20200803.11

Received: June 9, 2020; Accepted: June 23, 2020; Published: June 29, 2020

**Abstract:** In order to improve the accuracy and stability of bandgap reference output voltage, a bandgap reference circuit with high power supply rejection ratio and low temperature drift is designed based on 0.18um BCD technology. Based on the traditional bandgap voltage reference structure, this paper designs a current mirror cascade and a prereference circuit to supply power to the bandgap reference, and achieves a high power rejection ratio. At the same time, a PTAT<sup>2</sup> current generation circuit is designed to realize the second-order temperature compensation of the reference output voltage. The simulation results show that the power supply voltage is 5V, PSRR is - 80dB, the temperature changes from - 55°C to 125°C, and the reference voltage temperature coefficient is 4.27ppm /°C. The circuit is simple in structure and easy to integrate. It can be widely used in bandgap reference circuit design.

**Keywords:** Second Order Curvature Compensation, Low Temperature Drift, High Power Rejection Ratio

# 一种二阶曲率补偿的低温漂带隙基准电路设计

## 郭灿\*, 胥锐,潘军

中国电子科技集团公司第二十四研究所, 重庆, 中国

#### 邮箱

guoc@mixic.com.cn (郭灿), xur@mixic.com.cn (胥锐), panj@mixic.com.cn (潘军)

**摘要:**为了提高带隙基准输出电压的精度及其稳定性,基于0.18um BCD工艺,设计了一款高电源抑制比、低温漂的带隙基准电路。本文在传统的带隙基准电压源结构基础上,通过设计电流镜级联以及预基准电路为带隙基准供电,实现了高电源抑制比。同时设计了一种PTAT<sup>2</sup>电流产生电路,实现了基准输出电压的二阶温度补偿。仿真结果表明:电源电压为5V,PSRR为-80dB,温度从-55℃变化到125℃,基准电压温度系数为4.27ppm/℃。该电路结构简单,容易集成,可以广泛应用于带隙基准电路设计中。

关键词: 二阶曲率补偿, 低温漂, 高电源抑制比

#### 1. 引言

带隙基准电压是一种具有较高精度和稳定性的参考电压源,是模拟电路和数模混合电路中的核心模块之一,广泛应用于DC/DC、ADC、DAC以及DRAM等集成电路的设计中。带隙基准电路的设计是为了获得一个不随工艺参数、电源电压、温度变化而变化的基准电压,其性能的好坏直接影响到整个电路的稳定性。因此,设计一个高电源抑制比、低温漂的高性能基准电压源,在电路设计中显得尤为重要。

本文在传统的带隙基准电压源结构基础上,设计了一款高电源抑制比、低温漂的带隙基准电路。该电路采用 0.18um BCD工艺进行设计,电源电压为5V,PSRR为-80dB,温度从-55℃变化到125℃,基准电压温度系数为4.27ppm/℃。该电路结构简单,通过二阶曲率补偿的方式大大改善了基准输出电压在高温时的温度特性,降低了温度系数,最终输出较低温漂的基准电压,进一步提高了系统的稳定性。

#### 2. 电路结构与原理分析

双极性晶体管的基极-发射极电压 $V_{BE}$ 与温度之间并不是线性关系,其在参考温度下的泰勒级数展开式可以表示为[1]:

$$V_{RF} = V_{RF0} + b_1(t-t_0) + ... + b_n(t-t_0)^n$$

(1)

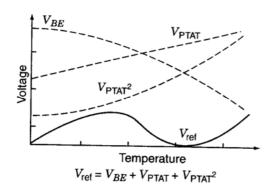

其中 $b_1$ ,  $b_2$ ... $b_n$ 为常数, $t_0$ 为参考温度,t为绝对温度。传统的带隙基准电压源只消除了 $V_{BE}$ 展开式中的一阶线性项  $b_1$ (t- $t_0$ ),与温度相关的高阶项并没有消除[2],因此基准电压的温漂仍然很大。本文设计的二阶曲率补偿电路,能够抵消 $V_{BE}$ 泰勒展开式中的一阶项和二阶项,只保留三阶及更高阶分量。实现此类补偿的方法就是用额外的电路产生 $PTAT^2$ (Proportional to Absolute Temperature,PTAT)项,以实现二阶温度补偿。采用二阶补偿的基准输出电压表达式为[3]:

$$V_{ref} = V_{BE} + V_{PTAT} + V_{PTAT^2} \tag{2}$$

图1 二阶补偿带隙基准温度特性曲线。

其中 $V_{PTAT}$ 电压与绝对温度成正比, $V_{PTAT}^2$ 电压与绝对温度平方成正比。

#### 3. 电路实现

#### 3.1. 二阶曲率补偿电路

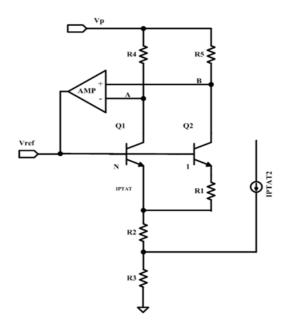

图2 二阶曲率补偿电路。

图2为一种基于经典带隙基准结构(Brokaw bandgap)[4]的二阶曲率补偿电路。三极管Q1、Q2的集电极通过运放嵌位,使得A、B两点电压相等。由于R4和R5是两个阻值相同且完全匹配的电阻,因此流过Q1、Q2的集电极电流相等,为I<sub>PTAT</sub>,则有:

$$V_{RE1} = V_{RE2} + I_{PTAT}R_1 \tag{3}$$

$$V_{BE} = \frac{V_T \ln I_C}{A_0 J_S} \tag{4}$$

其中 $I_c$ 表示流过晶体管集电极的电流, $A_0$ 表示晶体管 发射极面积, $J_s$ 为晶体管反相饱和电流[5]。将式(4)代入式(3)可得:

$$I_{PTAT} = \frac{V_T \ln N}{R_1} \tag{5}$$

由此形成的带隙基准电路, 其基准输出电压表达式为:

$$V_{ref} = V_{BE} + 2I_{PTAT}(R_2 + R_3) + I_{PTAT}^2 R_3$$

(6)

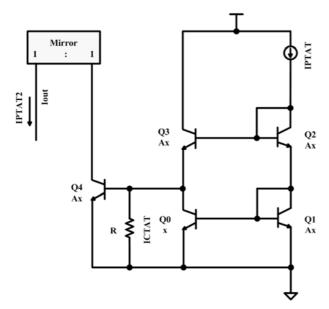

#### 3.2. PTAT<sup>2</sup>电流产生电路

与温度平方成比例关系的电流被称为PTAT<sup>2</sup>电流[6],图3为一种基于双极工艺实现的PTAT<sup>2</sup>电流产生电路,该电路利用PTAT电流和一些基极发射极环路来产生PTAT<sup>2</sup>电流。图中I<sub>CTAT</sub>(Complementary to Absolute Temperature, CTAT)是负温度系数的电流:

$$I_{CTAT} = \frac{V_{BE}}{R} \tag{7}$$

图3 PTAT<sup>2</sup>电流产生电路。

根据图3所示电路及KVL定律可推导出:

$$V_{BE4} + V_{BE3} = V_{BE1} + V_{BE2}$$

(8)

将式(4)代入式(8)可得:

$$\frac{V_T \ln I_{C4}}{AxJ_S} + \frac{V_T \ln I_{C3}}{AxJ_S} = \frac{V_T \ln I_{C1}}{AxJ_S} + \frac{V_T \ln I_{C2}}{AxJ_S}$$

(9)

$$I_{C4}*I_{C3}=I_{C1}*I_{C2}$$

(10)

其中:

$$I_{C1} = I_{C2} = I_{PTAT}$$

(11)

$$I_{C3} = I_{CTAT} + I_{PTAT} / A \tag{12}$$

将式(11)、(12)代入式(10)可得:

$$I_{OUT} = I_{C4} = \frac{I_{PTAT}^2}{I_{CTAT} + \frac{I_{PTAT}}{4}} = \frac{I_{PTAT}^2}{K}$$

(13)

其中IC3=K是一个与温度无关的电流:

$$K = I_{CTAT} + \frac{I_{PTAT}}{A} = \frac{V_{BE}}{R} + \frac{I_{PTAT}}{A}$$

(14)

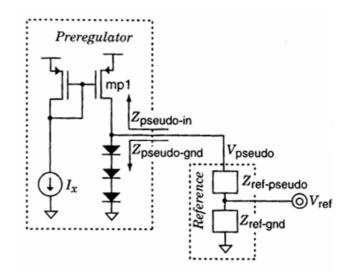

#### 3.3. 预基准电路

在开关电源控制电路中,受功率驱动级的影响,芯片内部供电有非常大的噪声以及尖峰扰动电压,因此在这种应用环境下,需要设计一个具有较高电源抑制比(Power Supply Rejection Ratio, PSRR)的带隙基准电路,以减小供电电压对基准输出电压的影响[7]。目前常用的方法就是采用电流镜级联以及预基准电路。图4为采用预基准实现高PSRR的电路示意图,其电源抑制比PSRR的计算方法为[8]:

$$PSRR = PSRR_{pre-reg} * PSRR_{reference}$$

(15)

$$PSRR = \frac{Z_{preudo-in} + Z_{preudo-gnd}}{Z_{preudo-gnd}} * \frac{Z_{ref-preudo} + Z_{ref-gnd}}{Z_{ref-gnd}}$$

(16)

其中 $Z_{preudo-in}$ 是从预基准输出到电源之间的阻抗, $Z_{preudo-gnd}$ 是从预基准输出到地之间的阻抗。 $Z_{ref-preudo}$ 是从 $V_{ref}$ 到预基准输出之间的阻抗, $Z_{ref-gnd}$ 是从 $V_{ref}$ 到地之间的阻抗。

图4 采用预基准实现高PSRR的电路示意图。

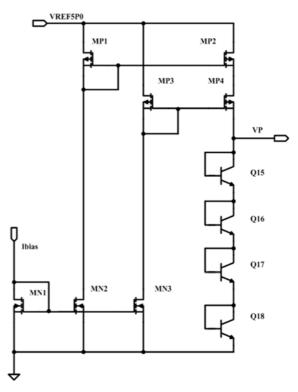

图5 预基准具体电路。

图5为预基准输出电压的具体电路,MP1和MP2为电流镜,MP3和MP4为电流镜,通过级联MP2和MP4电流源形成了预基准输出到电源之间的高阻抗通路[9],其阻抗

$$Z_{preudo-in} = g_{m4} r ds_4 r ds_2$$

(17)

4个BE结构成了预基准输出到地的低阻通路,其阻抗

$$Z_{preudo-gnd} = \frac{4V_T}{I_D}$$

(18)

由此可知Z<sub>preudo-gnd</sub>远小于Z<sub>preudo-in</sub>,从而达到了高PSRR 的设计目的。通过仿真,当VCC=5V时,在频率为1kHz 范围内PSRR为-80dB, 预基准输出电压为4个BE结电压(约 2.8V)。

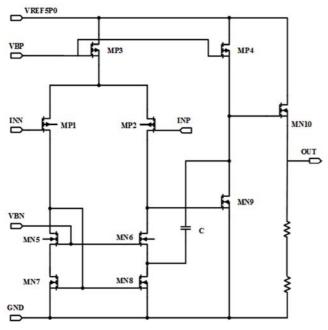

#### 3.4. 运算放大器电路

为了获得较高的增益,该运算放大器采用两级运放结构[10]。第一级的输入级采用差分输入,负载采用共源共栅的结构来提高第一级增益。电路的第一级增益为:

$$AV_1 = \operatorname{gm}_1 \times ((gm6 \times rds_6 \times rds_8) \parallel rds_2)$$

(19)

电路第二级采用共源放大器,负载为电流源负载,其增益为:

$$AV_2 = \operatorname{gm}_9 \times (r \operatorname{ds}_9 || r \operatorname{ds}_4) \tag{20}$$

电路总的增益为:

$$AV = AV_1 * AV_2 \tag{21}$$

电容C为密勒补偿电容,通过密勒补偿技术,使得主极点移动到较低的频率,次极点移动到较高的频率,基准在获得较大增益的同时还能保证很好的环路稳定性[11]。

图6 运算放大器电路原理图。

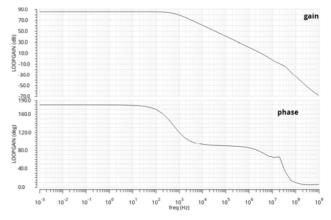

对该放大器采用0.18um的BCD工艺模型进行仿真,结果显示放大器的低频增益为85dB,相位裕度为80°,单位

增益带宽为8.1MHz。使得运放在具有较高的增益、较小的失调电压和噪声的同时有很好的环路稳定性。仿真结果如图7所示:

图7 运算放大器环路稳定性分析。

#### 4. 整体电路设计及其仿真

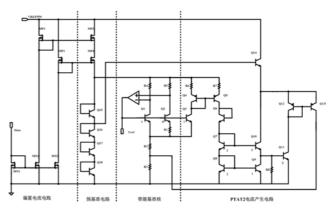

图8 带隙基准电路。

该电路包括偏置电流电路、预基准电路、带隙基准核电路、PTAT<sup>2</sup>电流产生电路,各功能模块已在前面有所介绍。传统的带隙基准电路中没有晶体管Q3,此处Q3与Q1组成电流镜,因此流过Q3的电流也是PTAT电流,再通过电流镜Q4、Q5将PTAT电流送到PTAT<sup>2</sup>电流产生电路中。由于Q3的影响,其基准输出电压计算公式为[12]:

$$V_{ref} = V_{BE1} + 3I_{PTAT}(R_2 + R_3) + I_{PTAT}^2 R_3$$

(22)

设计步骤如下:

根据系统功耗要求确定PTAT电流的大小,本文设计  $I_{PTAT}$ =2.734uA,进而根据公式(5)确定电阻 $R_1$ ≈20k。

电阻 $R_8$ 可以通过仿真确定其阻值,仿真方法就是改变  $R_8$ 的阻值,取当流过Q10集电极的电流在全温度范围内温度漂移达到最小时的电阻值即可。

确定电阻 $R_3$ 的取值,由于 $R_3$ 是设计来抵消BE二极管二阶温度项,因此 $R_3$ 的阻值必须满足以下条件[13]:

$$\frac{\partial^2 V_{ref}}{\partial^2 T} + 2I_{PTAT^2} R_3 = 0 \tag{23}$$

D、设计 $R_2$ 的值,可以借助仿真器进行仿真,改变 $R_2$ 的阻值将 $V_{ref}$ 的温度系数调到最优点。

本文基于0.18um的BCD工艺模型,采用spectre仿真器对该带隙基准电路进行模拟仿真。仿真电源电压范围为3.3V-6.0V,温度范围为-55 $\mathbb{C}$ -125 $\mathbb{C}$ 。

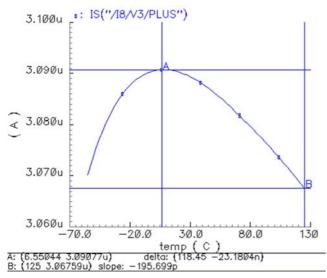

图9 典型条件下晶体管Q10的集电极电流温度特性。

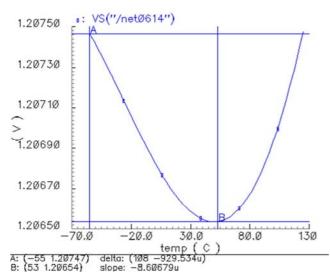

图10 典型条件下基准输出电压温度特性。

典型工作条件下(VCC=5V, TT CORNER),流过晶体管Q10集电极电流在全温度范围内变化23nA,可以认为该电流是一个与温度无关的电流,基准输出电压为1.206V,基准输出电压在全温度范围内变化0.929mV,温漂为4.27ppm/°C。

考虑到电路的实际应用环境,本文对工艺、电压、温度等变量进行拉偏仿真[14],全温全电压条件下基准电压以及温漂仿真结果如下列各表所示:

表1 不同CORNER下仿真结果(VCC=5.0V)。

| CORNER    | TT    | SS    | SF    | FS    | FF    |

|-----------|-------|-------|-------|-------|-------|

| Vref(V)   | 1.206 | 1.185 | 1.201 | 1.215 | 1.230 |

| 温漂(ppm/℃) | 4.27  | 3.53  | 2.19  | 4.52  | 5.11  |

表2 不同VCC下仿真结果(CORNER=TT)。

| VCC       | 3.3V  | 5V    | 6V    |  |

|-----------|-------|-------|-------|--|

| Vref(V)   | 1.206 | 1.206 | 1.207 |  |

| 温漂(ppm/℃) | 4.27  | 4.27  | 4.28  |  |

从仿真结果可以看出,在所有工艺CORNER下,电源电压供电范围从3.3V到6.0V,温度范围从-55°C到125°C,本文所设计的带隙基准电路,基准输出电压最小值为1.185V,最大值为1.230V,基准输出电压最大偏差约2%,温漂最大值为5.11 ppm/°C,最小值为2.19 ppm/°C。

#### 5. 结论

本文提出了一种高电源抑制比、低温漂的带隙基准电路,基于传统的带隙基准核心结构,通过电流镜级联以及预基准电路为带隙基准供电,能够实现高电源抑制比,减小供电电压对基准输出电压的影响;同时设计了一种PTAT<sup>2</sup>电流产生电路,大大改善了基准输出电压在高温时的温度特性,实现了基准输出电压的二阶温度补偿。仿真结果表明:当VCC=5V时,在频率为1kHz范围内PSRR为-80dB,基准输出电压的温度系数为4.27ppm/℃。该电路结构简单,容易集成,可以广泛应用于带隙基准电路设计中[15]。

### 参考文献

- RINCONMORA G A. Voltage references-from diodes to precision high-order bandgap circuits [M]. USA: IEEE Press, 2002: 45-118.

- [2] 梁希,刘文平,刘志. 一种高阶曲率补偿带隙基准的原理 与实现[J].微电子学与计算机,2012,29(10): 117-120.

- [3] 张万东,陈宏,王一鹏,等. 高电源抑制比和高阶曲率补偿带隙电压基准源[J]. 微电子学,2011,41(1):57-60.

- [4] PAUL R.GRAY, PAUL J.HURST. 模拟集成电路的分析与设计[M]. 北京:高等教育出版社, 2003.

- [5] 张博亮. 一种基于LDO稳压器的带隙基准电压源设计 [J]. 电子设计工程, 2015, 23(24): 64—66.

- [6] Phillip.E. Allen, Douglas R. Holberg. CMOS模拟集成电路设计[M]. 北京:电子工业出版社.2002.

- [7] 杨金梅, 唐祯安. 采用曲率补偿的高PSRR基准电压源 [J]. 微电子学 , 2009, 39(1):34-37.

- [8] 王文建. 基于BiCMOS工艺可修调的高精度低温度系数带隙基准源设计[J]. 传感技术学报,2017,30(5): 674-677.

- [9] Lai Xinquan, Xu Ziyou, Li Yanming, et al.A CMOS Piecewise Curvature-compensated Voltage Reference [J]. Microelectronics Journal, 2009, 40(1): 39-45.

- [10] RAZAVI. B. 模拟CMOS集成电路设计[M].陈贵灿,等译。 西安: 西安交通大学出版社,2003.

- [11] WANG H Y, LAI X Q, LI Y S, et al. A CMOS bandgap reference corrected by second degree curve[J]. Chinese Journal of Electron Devices, 2007, 30(4): 1 155-1 158.

- [12] 张宗航,赵毅强,耿俊峰.一种二阶曲率补偿带隙基准电压源[J].微电子学与计算机,2012,29(5):15-19.

- [13] 唐宇, 冯全源. 一种低温漂低功耗带隙基准的设计[J].电子元件与材料, 2014, 33(2): 30-33.

- [14] Zhou Zekun, Ming Xin, Zhang Bo, et al. A novel precision curvature compensated bandgap reference[J]. Journal of Semiconductors, 2010,31(1):015010-1-015010-4.

- [15] 周玮,吴贵能,李儒章.一种二阶补偿的CMOS带隙基准电压源[J]. 重庆邮电大学学报,2009,21(1):78.82.